Utilize FRAM's non-volatile and fast-write characteristics to ensure data integrity and responsiveness in critical systems

A

A

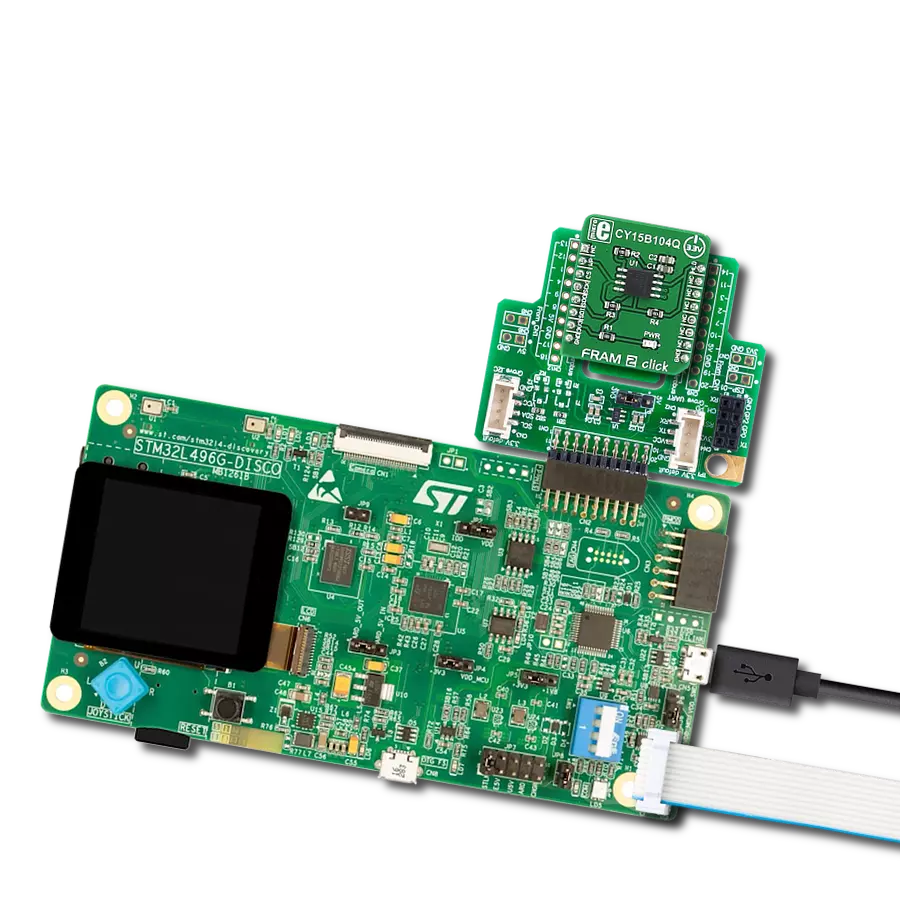

Hardware Overview

How does it work?

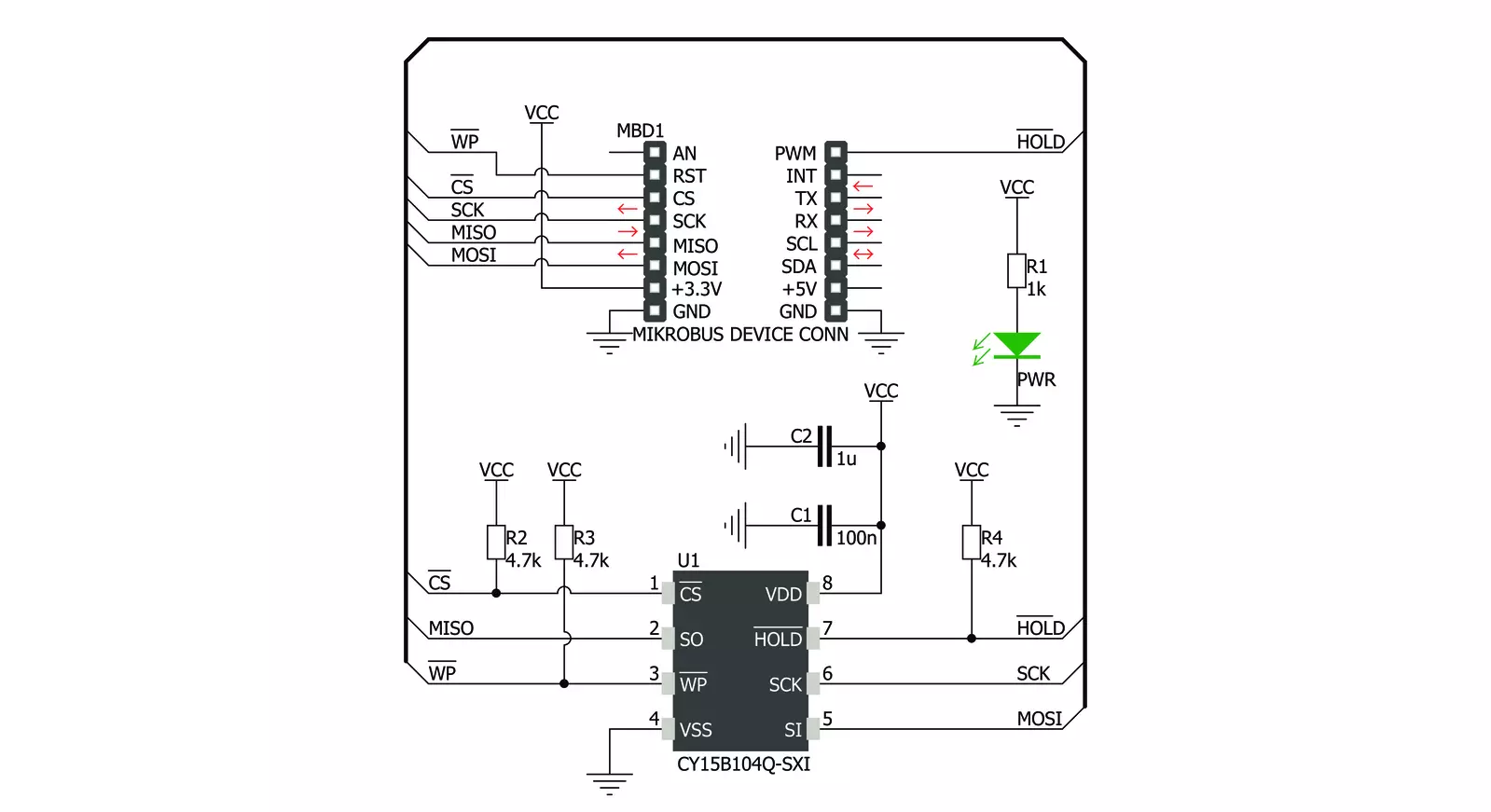

FRAM 2 Click is based on the CY15B104Q, a 4 Mbit serial ferroelectric (FRAM) module from Infineon. It contains 4,194,304 bits of memory, organized in 524,288 byes. This means that the storage area contains 512 KB of address space. This memory IC is manufactured using ferroelectric technology, which has many advantages over the conventional technologies used for manufacturing EEPROM and FLASH memory modules. Ferroelectric technology is still being developed and perfected, but the advantages have already been demonstrated. This technology exploits the properties of ferroelectric materials to retain the electric field after exposure, the same way the ferromagnetic materials retain their magnetic field. This phenomenon is employed to polarize the FRAM cells and store the information. One area that still needs improvement is the thermal instability, especially at high temperatures. When the ferroelectric material reaches the Curie temperature, its properties are degraded. Therefore, the high temperature might damage the content of the FRAM module. This is illustrated by the data retention period: while working at 85˚C, the data retention period is reduced to 10 years. At 65˚C, the data retention period stretches to over 150 years. Still, combined with the endurance of 1014 read/write cycles at bus write speed, this type of memory still represents an ideal solution for applications with frequent writing to non-volatile memory locations. This Click board™ uses the SPI communication protocol, allowing fast serial clock rates. The device employs certain protection mechanisms to ensure reliable data transactions and avoid accidental writing to the memory array. The WEL bit must be set before

writing any data to the IC, which modifies registers or the array itself. This bit is cleared after or during every memory modification instruction. Therefore, every memory modification instruction must be prefixed with the Write Enable (WREN) instruction that sets this bit to 1. This mechanism ensures that only the intended write instruction will be executed. The host MCU initiates Communication with the device, which drives the chip select pin (#CS on the schematic) to a LOW logic level. This pin is routed to the mikroBUS™ CS pin. The next byte of information can be either command or data. Usually, the first byte is the instruction (command) followed by the memory address. Depending on the command sent, either the memory is written to or read from the specific memory address. The memory address on this device is 19-bit (0x00000 to 0x7FFFF), and therefore, it is sent by 3 bytes. Several instruction codes can be sent after the CS pin is driven to a LOW logic level. These include Write Enable, Write to the memory array, Read from the memory array, Write Status Register, Read Status Register, and so on. For a full list of commands and their detailed description, please refer to the datasheet of the CY15B104Q IC. When using the write-to-array instruction, it is possible to write the whole array while keeping the CS line to a LOW logic level, as the internal address pointer will increase with each received byte of data. Once the end of the array is reached (address 0x7FFFF), the internal pointer will roll over from the beginning (0x00000). An obvious advantage over the traditional EEPROM can be observed here: on a traditional EEPROM, the memory is organized in pages, usually 256 bytes long, which allows

buffering of the data because of the inherently slow write operation. The FRAM memory does not use pages because the memory is written faster than the SPI bus can deliver new information (the data is written at bus speed). Therefore, no buffering is required, and the whole array can be sequentially written. The CY15B104Q includes the write protection of the specific parts or the whole memory array. The write protection consists of two bits in the Status Register (B0, B1). The Write Status Register instruction can set or reset these bits. B0 and B1 bits control the write-protect status of the memory array (from one-quarter to full memory array protection). These bits are non-volatile, and their state is retained between the power cycles. The #WP pin is used to lock the Status Register. When this pin is driven to a LOW level, no further modifications to the Status register are possible, and the instructions used to change bits in this register (Write Enable and Write Status Register) are completely ignored. Driving this pin to a LOW state effectively acts as the hardware memory write-protect lock mechanism. The WPEN bit of the status register can completely turn off this pin: if the WPEN bit is cleared (0), this pin will not affect the CY15B104Q IC. The #WP pin is routed to the mikroBUS™ RST pin and labeled as WP. The FRAM 2 click allows hold of the communication in progress. If the #HOLD pin is driven to a LOW logic level on the LOW pulse of the serial clock signal (SCK), the communication will be paused but not aborted. Driving this pin to a HIGH logic level will resume the data transfer. This pin is routed to the mikroBUS™ PWM pin, labeled as HLD.

Features overview

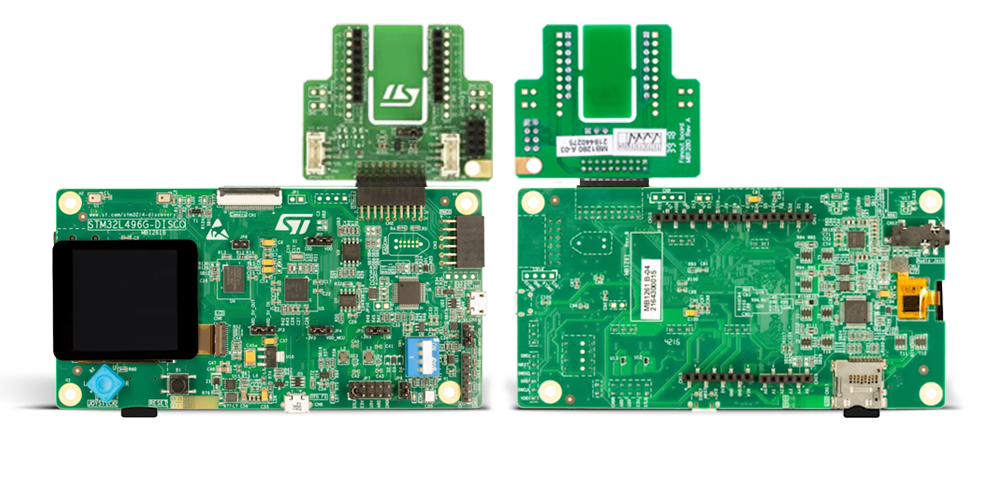

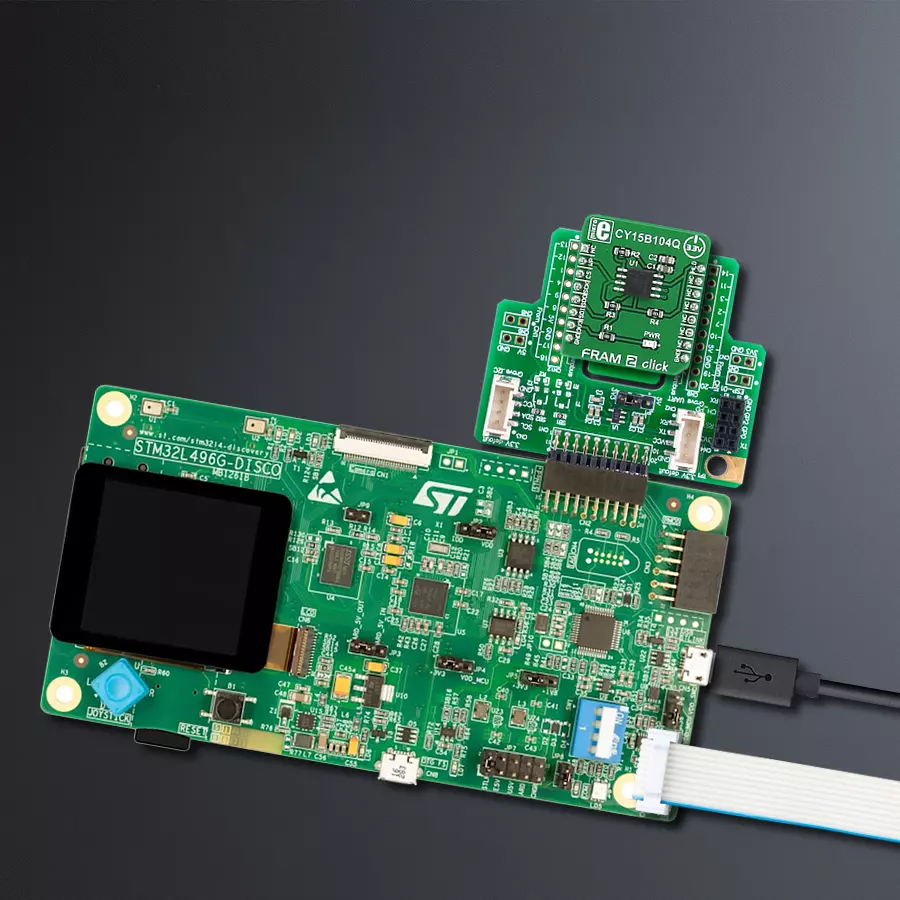

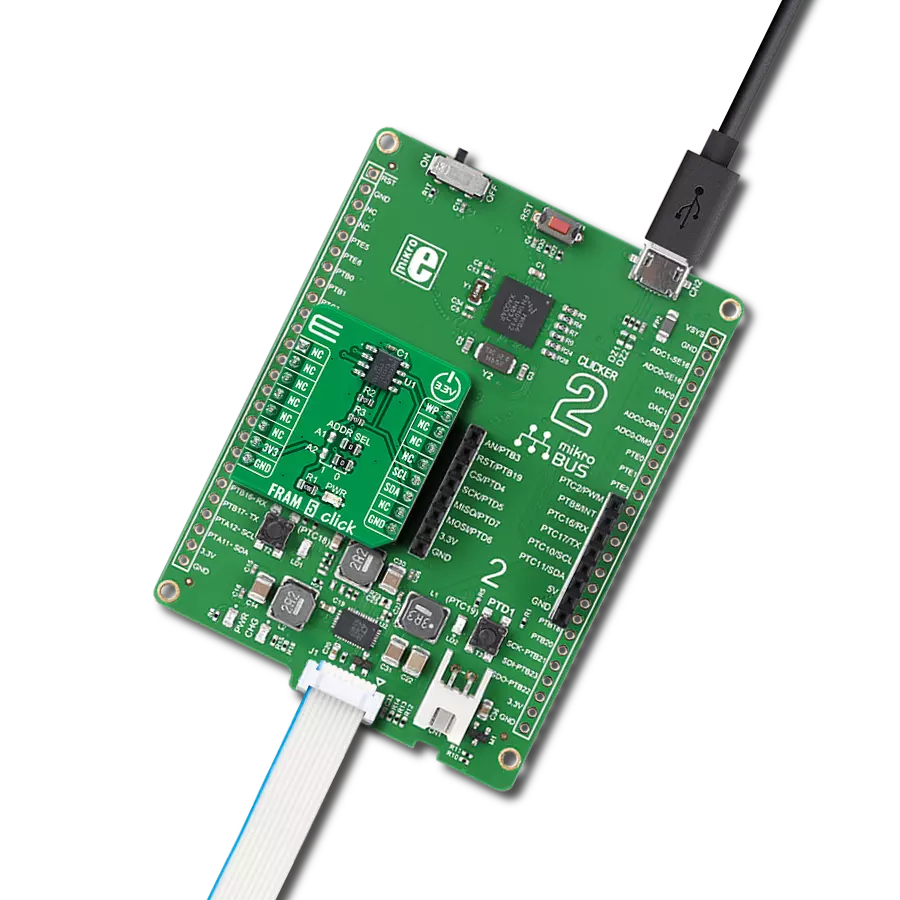

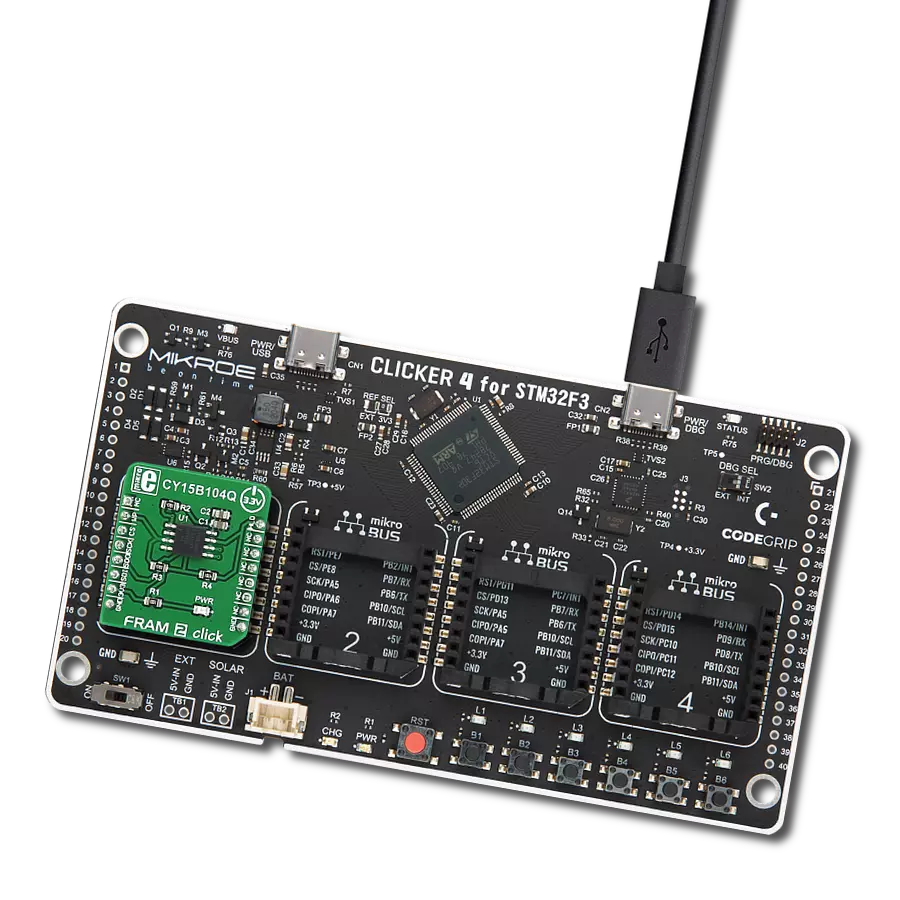

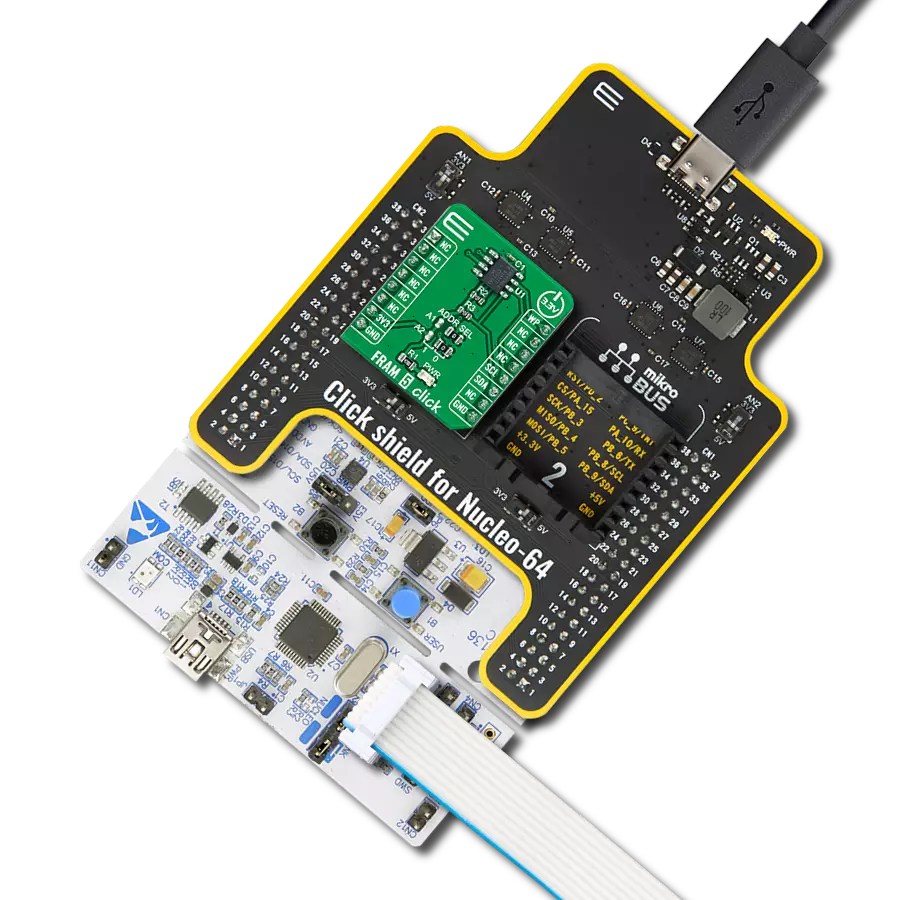

Development board

The 32L496GDISCOVERY Discovery kit serves as a comprehensive demonstration and development platform for the STM32L496AG microcontroller, featuring an Arm® Cortex®-M4 core. Designed for applications that demand a balance of high performance, advanced graphics, and ultra-low power consumption, this kit enables seamless prototyping for a wide range of embedded solutions. With its innovative energy-efficient

architecture, the STM32L496AG integrates extended RAM and the Chrom-ART Accelerator, enhancing graphics performance while maintaining low power consumption. This makes the kit particularly well-suited for applications involving audio processing, graphical user interfaces, and real-time data acquisition, where energy efficiency is a key requirement. For ease of development, the board includes an onboard ST-LINK/V2-1

debugger/programmer, providing a seamless out-of-the-box experience for loading, debugging, and testing applications without requiring additional hardware. The combination of low power features, enhanced memory capabilities, and built-in debugging tools makes the 32L496GDISCOVERY kit an ideal choice for prototyping advanced embedded systems with state-of-the-art energy efficiency.

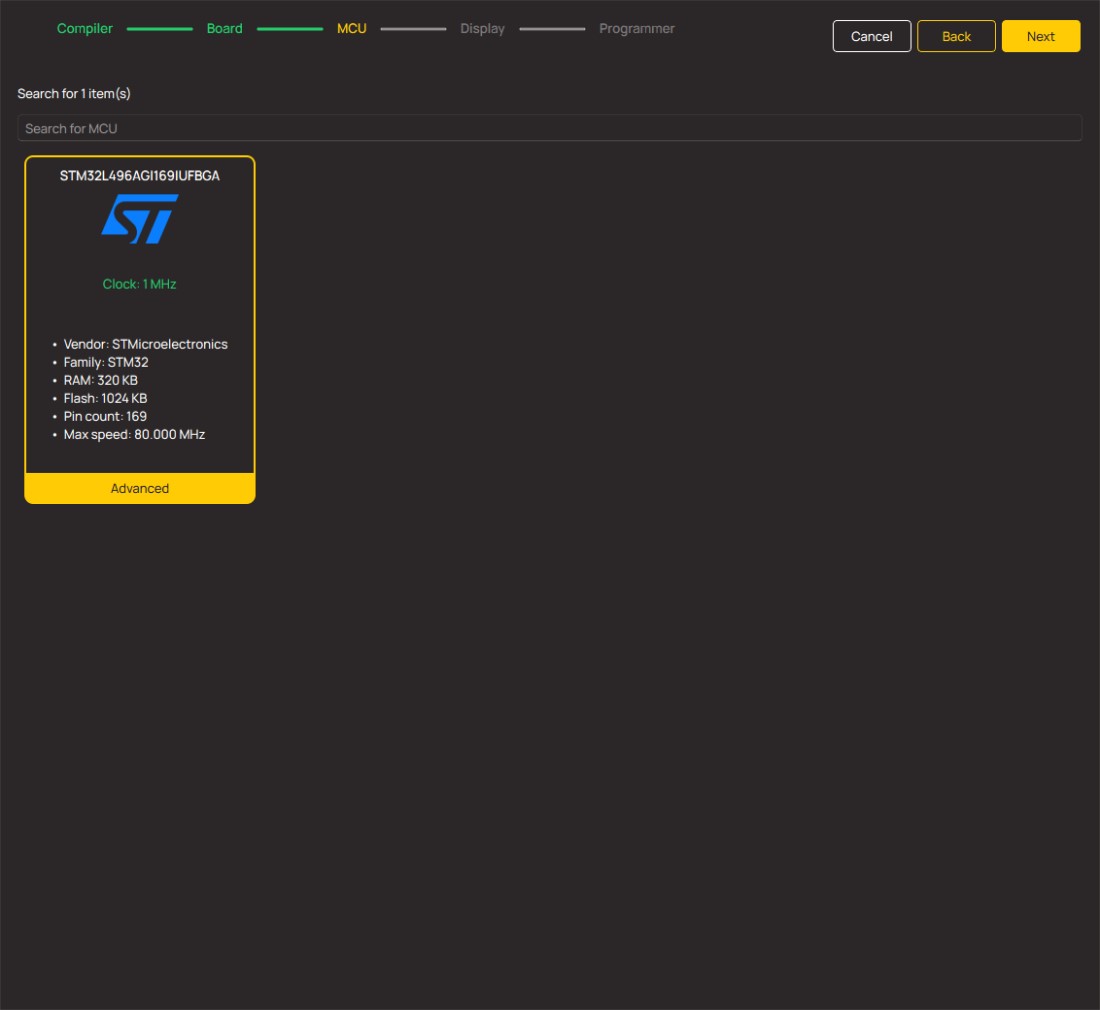

Microcontroller Overview

MCU Card / MCU

Architecture

ARM Cortex-M4

MCU Memory (KB)

1024

Silicon Vendor

STMicroelectronics

Pin count

169

RAM (Bytes)

327680

Used MCU Pins

mikroBUS™ mapper

Take a closer look

Click board™ Schematic

Step by step

Project assembly

Software Support

Library Description

This library contains API for FRAM 2 Click driver.

Key functions:

fram2_read- This function reads content from address and saves it to bufferfram2_write- This function writes content from buffer to addressfram2_read_status- This function reads content of FRAM status register

Open Source

Code example

The complete application code and a ready-to-use project are available through the NECTO Studio Package Manager for direct installation in the NECTO Studio. The application code can also be found on the MIKROE GitHub account.

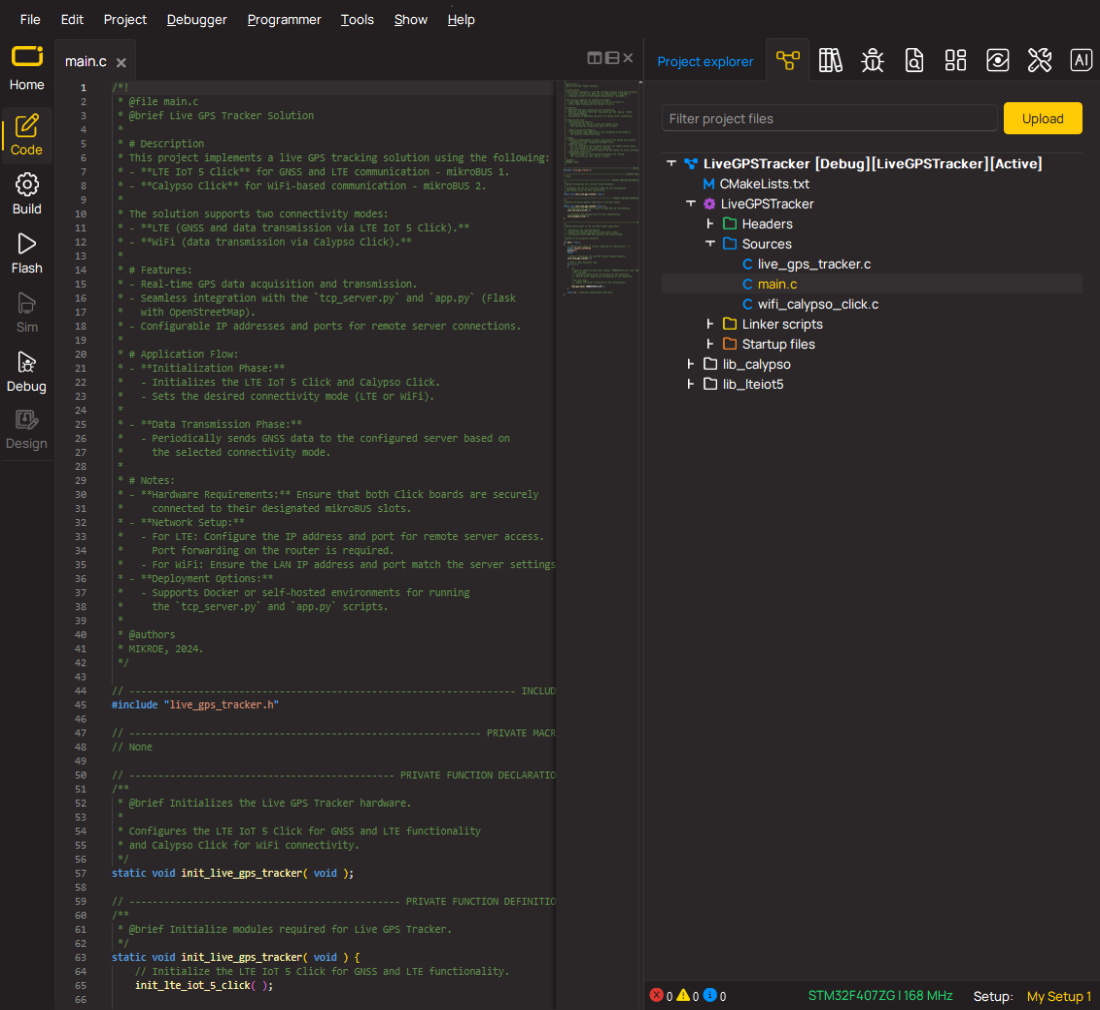

/*!

* \file

* \brief FRAM2 Click example

*

* # Description

* This example performs write & read operation to certain register.

*

* The demo application is composed of two sections :

*

* ## Application Init

* Initiazlize device and enable write operation.

*

* ## Application Task

* Write value 42 to register 0x10 and check if operation was done properly.

*

* *note:*

* data_to_write variable is declared as const, so compiler may warn user

* about 'suspisuous pointer conversion'. Note it is the case only with this

* code snippet but user has freedom to use driver functions as he wishes.

*

* \author MikroE Team

*

*/

// ------------------------------------------------------------------- INCLUDES

#include "board.h"

#include "log.h"

#include "fram2.h"

#include <string.h>

// ------------------------------------------------------------------ VARIABLES

static fram2_t fram2;

static log_t logger;

static uint8_t data_to_write[ 3 ] = { '4', '2', 0 };

static uint8_t read_buf [ 32 ];

static uint32_t test_addr;

// ------------------------------------------------------ APPLICATION FUNCTIONS

void application_init ( void )

{

log_cfg_t log_cfg;

fram2_cfg_t cfg;

/**

* Logger initialization.

* Default baud rate: 115200

* Default log level: LOG_LEVEL_DEBUG

* @note If USB_UART_RX and USB_UART_TX

* are defined as HAL_PIN_NC, you will

* need to define them manually for log to work.

* See @b LOG_MAP_USB_UART macro definition for detailed explanation.

*/

LOG_MAP_USB_UART( log_cfg );

log_init( &logger, &log_cfg );

log_info( &logger, "---- Application Init ----" );

// Click initialization.

fram2_cfg_setup( &cfg );

FRAM2_MAP_MIKROBUS( cfg, MIKROBUS_1 );

fram2_init( &fram2, &cfg );

fram2_default_cfg ( &fram2 );

}

void application_task ( void )

{

log_info( &logger, "Writing value 42 into register 0x10..." );

test_addr = 0x0010;

fram2_write( &fram2, test_addr, data_to_write, 3 );

Delay_ms ( 200 );

log_info( &logger, "Reading from register 0x10..." );

memset( read_buf, 0, 32 );

Delay_ms ( 500 );

fram2_read( &fram2, test_addr, read_buf, 3 );

log_printf ( &logger, "Read value: %s\r\n\n", read_buf );

Delay_ms ( 500 );

}

int main ( void )

{

/* Do not remove this line or clock might not be set correctly. */

#ifdef PREINIT_SUPPORTED

preinit();

#endif

application_init( );

for ( ; ; )

{

application_task( );

}

return 0;

}

// ------------------------------------------------------------------------ END

Additional Support

Resources

Category:FRAM