Experience unmatched timing precision by integrating a reliable clock generator into your solution

A

A

Hardware Overview

How does it work?

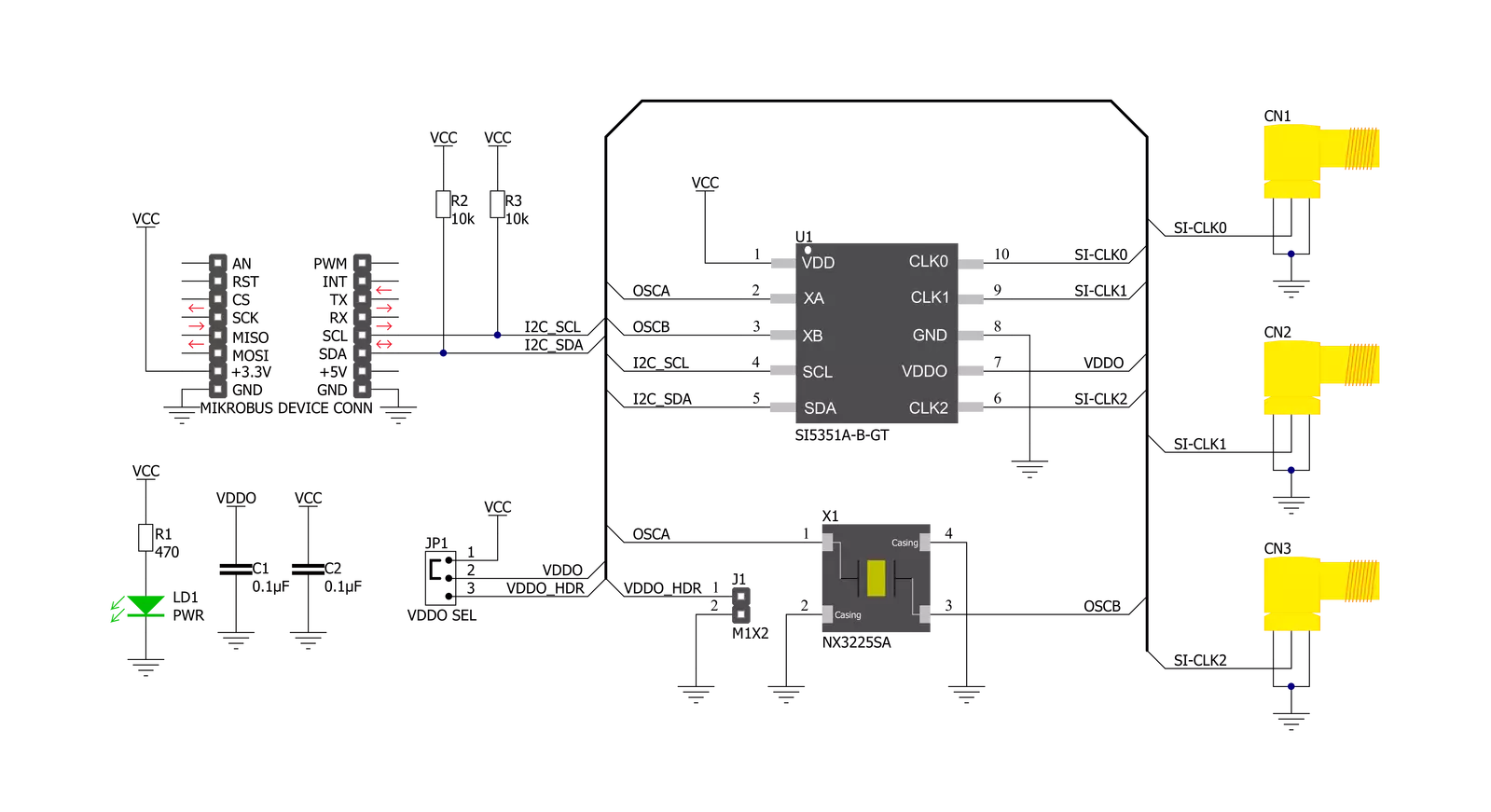

Clock Gen Click is based on the Si5351A, a versatile I2C programmable clock generator ideally suited for replacing crystals, crystal oscillators, VCXOs, PLLs, and buffers. The Si5351A consists of an input, two syntheses, and an output stage. The input stage accepts an external crystal (XTAL on XA and XB pins). The first stage of synthesis multiplies the input frequencies to a high-frequency intermediate clock, while the second stage of synthesis uses high-resolution MultiSynth fractional dividers to generate the desired output frequencies. Additional integer division is provided at the output stage for generating output frequencies as low as 2.5 kHz. Crosspoint switches at each synthesis stage allow total flexibility in routing any of the inputs to any of the outputs. Because of this high resolution and flexible synthesis architecture, the Si5351A can generate synchronous or free-running non-integer related clock frequencies at each output, enabling one device to synthesize clocks for multiple clock domains in a design. The Si5351A uses a fixed-frequency standard AT-cut crystal to reference the internal oscillator. The oscillator's output can

provide a free-running reference to one or both PLLs for generating asynchronous clocks. The oscillator's output frequency operates at the crystal frequency of 25 MHz. Internal load capacitors are provided to eliminate the need for external components when connecting a crystal to the Si5351A. The total internal XTAL load capacitance (CL) can be selected as 0, 6, 8, or 10 pF. The Si5351A uses two stages of synthesis to generate its final output clocks. The first stage uses PLLs to multiply the lower-frequency input references to a high-frequency intermediate clock. The second stage uses high-resolution MultiSynth fractional dividers to generate the required output frequencies. Only two unique frequencies above 112.5 MHz can be simultaneously output. For example, 125 MHz (CLK0), 130 MHz (CLK1), and 150 MHz (CLK2) are not allowed. Both PLLs are locked to the same source (XTAL). The crosspoint switch at the input of the second stage allows any of the MultiSynth dividers to connect to PLLA or PLLB. This flexible synthesis architecture allows any of the outputs to generate synchronous or non-synchronous clocks, with spread spectrum or

without spread spectrum, and with the flexibility of generating non-integer-related clock frequencies at each output. Frequencies down to 2.5 kHz can be generated by applying the R divider at the output of the Multisynth. All output drivers generate CMOS level outputs with a single output voltage supply pin (VDDO), allowing a different voltage signal level (1.8, 2.5, or 3.3 V) at the output banks. The output voltage level selection can be chosen by moving an SMD jumper labeled VDDO SEL to an appropriate position (3V3 or EXT). If 3V3 is chosen, the VDDO is supplied by the board. Otherwise, an external supply must be connected to the voltage level supply pin. This Click board™ uses the I2C communication interface and can be operated only with a 3.3V logic voltage level. The board must perform appropriate logic voltage level conversion before using MCUs with different logic levels. Also, it comes equipped with a library containing functions and an example code that can be used, as a reference, for further development.

Features overview

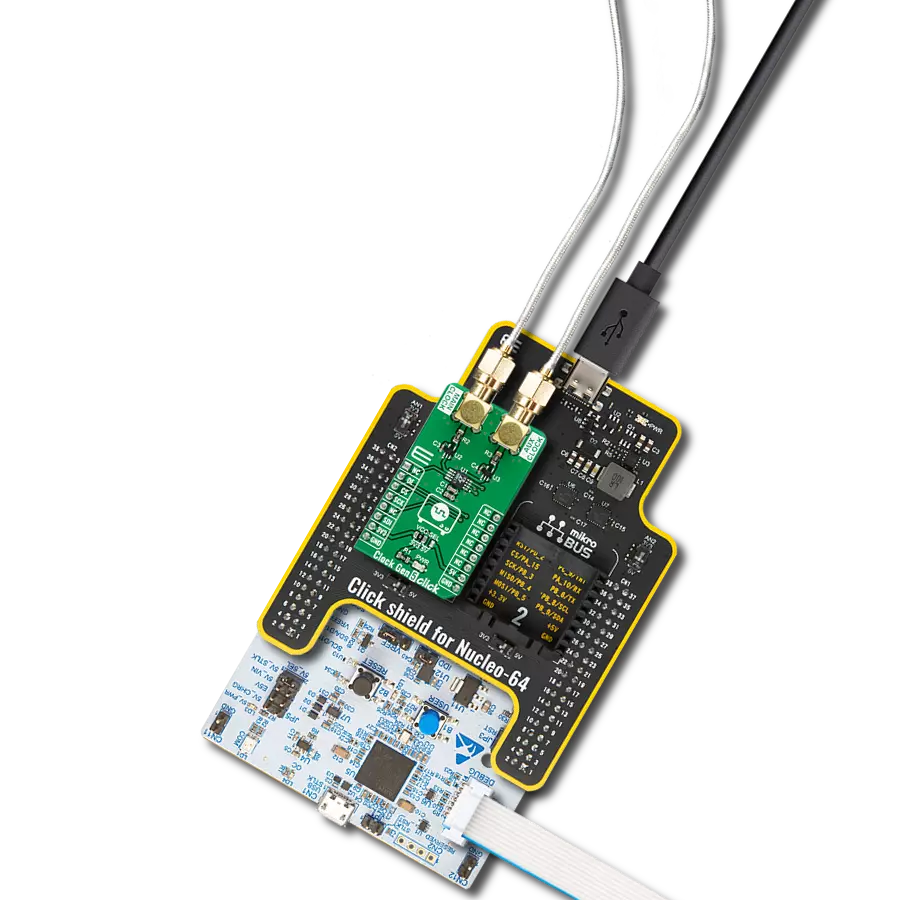

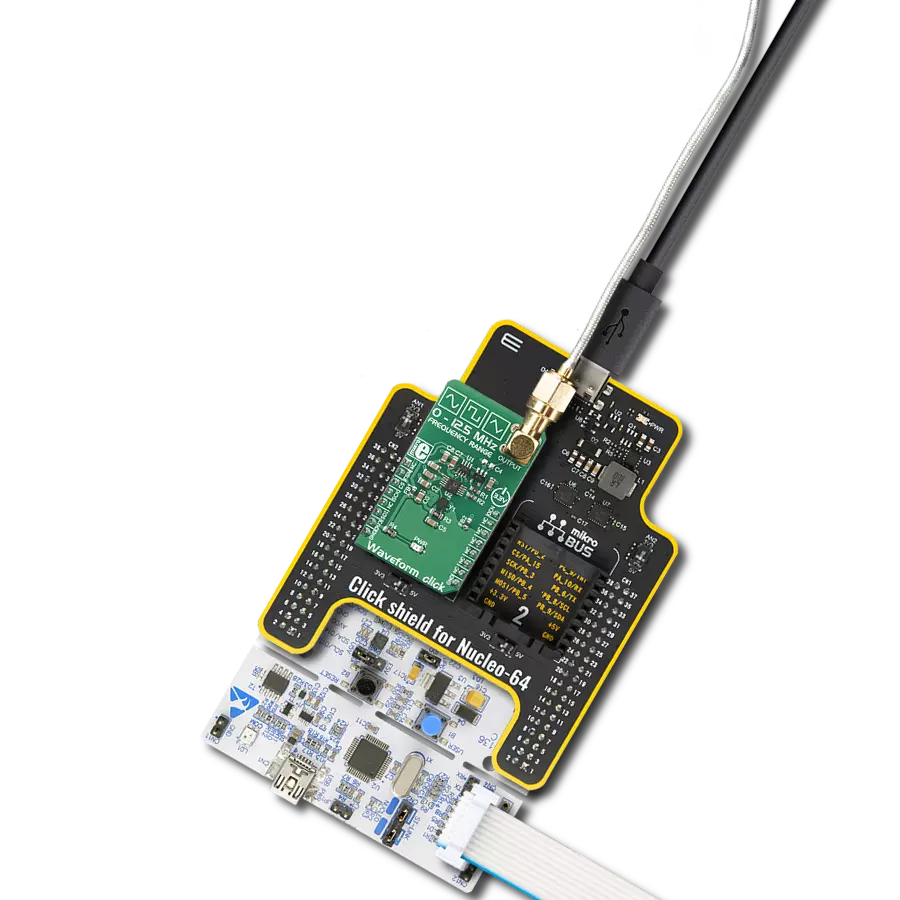

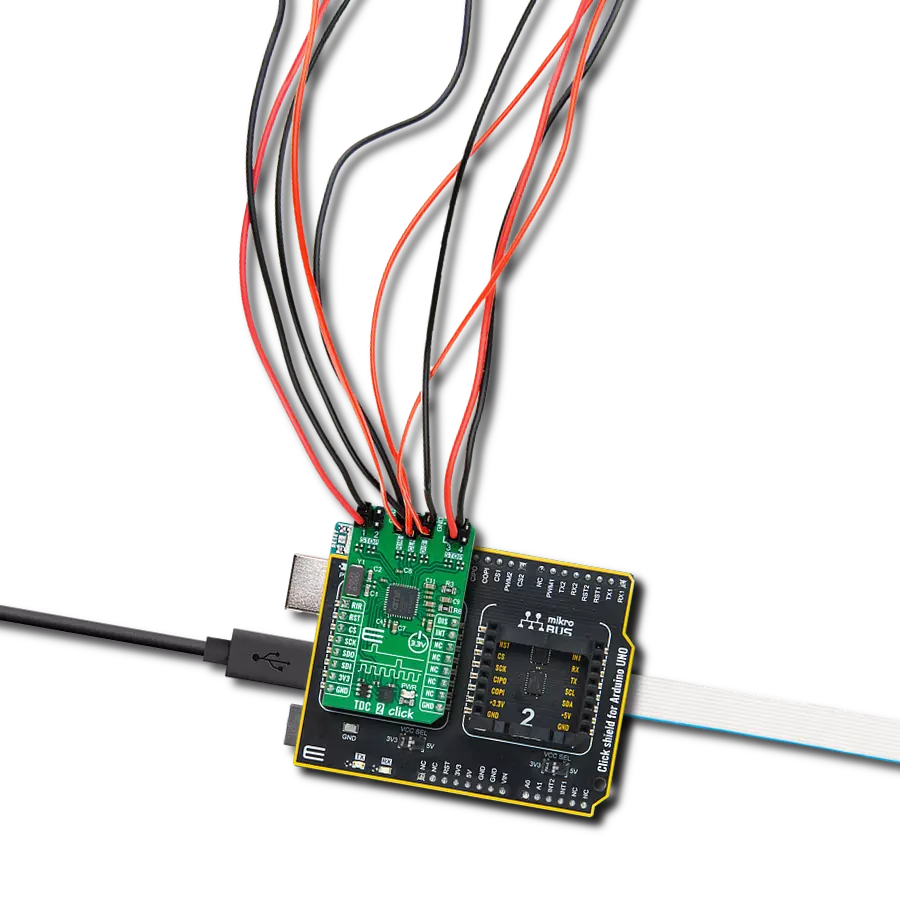

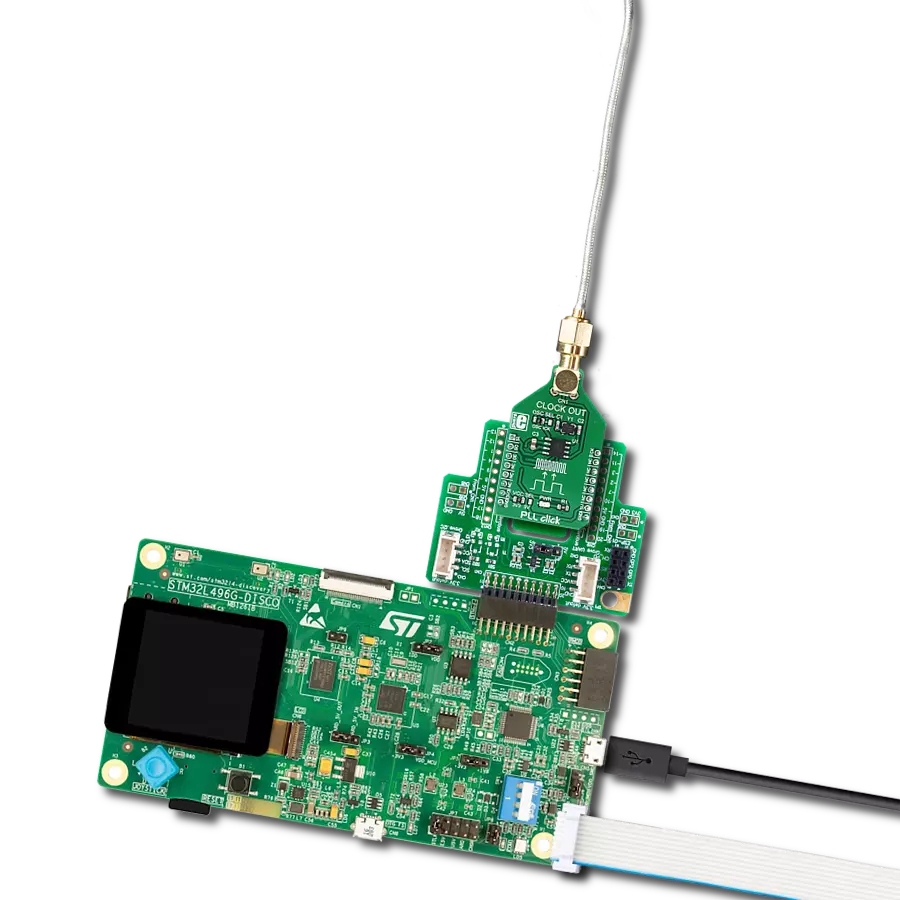

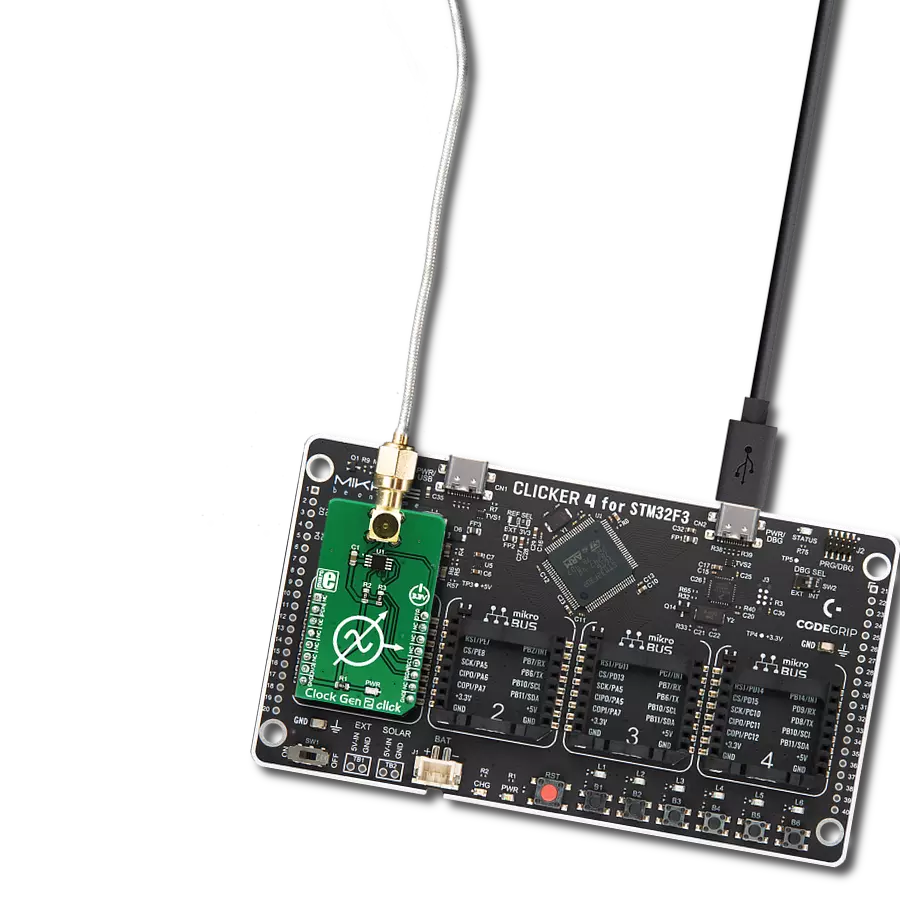

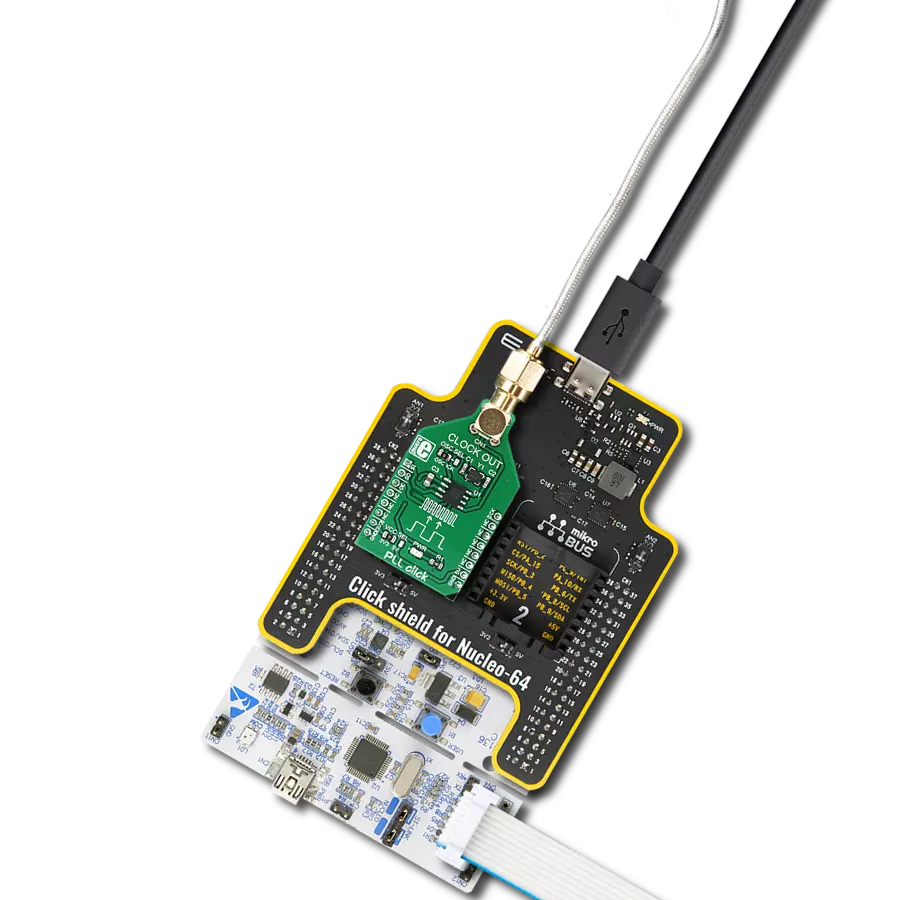

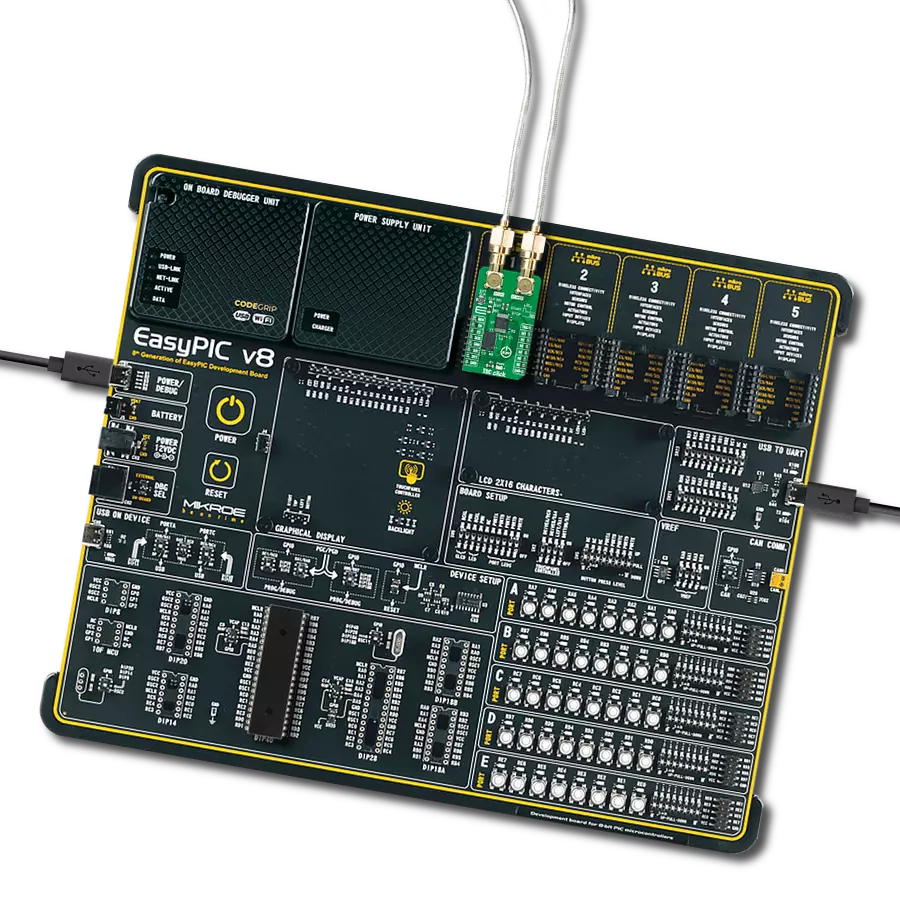

Development board

Clicker 2 for Kinetis is a compact starter development board that brings the flexibility of add-on Click boards™ to your favorite microcontroller, making it a perfect starter kit for implementing your ideas. It comes with an onboard 32-bit ARM Cortex-M4F microcontroller, the MK64FN1M0VDC12 from NXP Semiconductors, two mikroBUS™ sockets for Click board™ connectivity, a USB connector, LED indicators, buttons, a JTAG programmer connector, and two 26-pin headers for interfacing with external electronics. Its compact design with clear and easily recognizable silkscreen markings allows you to build gadgets with unique functionalities and

features quickly. Each part of the Clicker 2 for Kinetis development kit contains the components necessary for the most efficient operation of the same board. In addition to the possibility of choosing the Clicker 2 for Kinetis programming method, using a USB HID mikroBootloader or an external mikroProg connector for Kinetis programmer, the Clicker 2 board also includes a clean and regulated power supply module for the development kit. It provides two ways of board-powering; through the USB Micro-B cable, where onboard voltage regulators provide the appropriate voltage levels to each component on the board, or

using a Li-Polymer battery via an onboard battery connector. All communication methods that mikroBUS™ itself supports are on this board, including the well-established mikroBUS™ socket, reset button, and several user-configurable buttons and LED indicators. Clicker 2 for Kinetis is an integral part of the Mikroe ecosystem, allowing you to create a new application in minutes. Natively supported by Mikroe software tools, it covers many aspects of prototyping thanks to a considerable number of different Click boards™ (over a thousand boards), the number of which is growing every day.

Microcontroller Overview

MCU Card / MCU

Architecture

ARM Cortex-M4

MCU Memory (KB)

1024

Silicon Vendor

NXP

Pin count

121

RAM (Bytes)

262144

Used MCU Pins

mikroBUS™ mapper

Take a closer look

Click board™ Schematic

Step by step

Project assembly

Software Support

Library Description

This library contains API for Clock Gen Click driver.

Key functions:

clockgen_set_frequency- This function sets clock dividerclockgen_setup_pll- This function sets pllclockgen_setup_multisyinth- This function sets clock frequency on specific clock

Open Source

Code example

The complete application code and a ready-to-use project are available through the NECTO Studio Package Manager for direct installation in the NECTO Studio. The application code can also be found on the MIKROE GitHub account.

/*!

* \file

* \brief ClockGen Click example

*

* # Description

* Clock Gen Click represent a replacement for crystals, crystal oscillators, VCXOs, phase-locked

* loops (PLLs), and fanout buffers. This Click features an I2C configurable clock generator

* based on a PLL + high resolution MultiSynth fractional divider architecture which can generate

* any frequency up to 200 MHz with 0 ppm error. The chip on Click is capable of generating

* synchronous or free-running non-integer related clock frequencies at each of its outputs

* (CLK0, CLK1, and CLK2), enabling one device to synthesize clocks for multiple clock domains in a design.

*

* The demo application is composed of two sections :

*

* ## Application Init

* Configures device to default function that enables clock 0 and disables all others.

*

* ## Application Task

* Changes 4 different frequency in span of 5 seconds.

*

*

* \author MikroE Team

*

*/

// ------------------------------------------------------------------- INCLUDES

#include "board.h"

#include "log.h"

#include "clockgen.h"

// ------------------------------------------------------------------ VARIABLES

static clockgen_t clockgen;

static log_t logger;

// ------------------------------------------------------ APPLICATION FUNCTIONS

void application_init ( void )

{

log_cfg_t log_cfg;

clockgen_cfg_t cfg;

/**

* Logger initialization.

* Default baud rate: 115200

* Default log level: LOG_LEVEL_DEBUG

* @note If USB_UART_RX and USB_UART_TX

* are defined as HAL_PIN_NC, you will

* need to define them manually for log to work.

* See @b LOG_MAP_USB_UART macro definition for detailed explanation.

*/

LOG_MAP_USB_UART( log_cfg );

log_init( &logger, &log_cfg );

log_info( &logger, "---- Application Init ----" );

// Click initialization.

clockgen_cfg_setup( &cfg );

CLOCKGEN_MAP_MIKROBUS( cfg, MIKROBUS_1 );

clockgen_init( &clockgen, &cfg );

clockgen_default_cfg( &clockgen );

Delay_ms ( 500 );

}

void application_task ( void )

{

clockgen_set_frequency( &clockgen, CLOCKGEN_CLOCK_0, CLOCKGEN_PLLA, 1 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

clockgen_set_frequency( &clockgen, CLOCKGEN_CLOCK_0, CLOCKGEN_PLLA, 3 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

clockgen_set_frequency( &clockgen, CLOCKGEN_CLOCK_0, CLOCKGEN_PLLA, 10 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

clockgen_set_frequency( &clockgen, CLOCKGEN_CLOCK_0, CLOCKGEN_PLLA, 5 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

Delay_ms ( 1000 );

}

int main ( void )

{

/* Do not remove this line or clock might not be set correctly. */

#ifdef PREINIT_SUPPORTED

preinit();

#endif

application_init( );

for ( ; ; )

{

application_task( );

}

return 0;

}

// ------------------------------------------------------------------------ END

Additional Support

Resources

Category:Clock generator