Experience the perfect harmony of performance and peace of mind with nvSRAM, the ultimate memory solution for critical applications

A

A

Hardware Overview

How does it work?

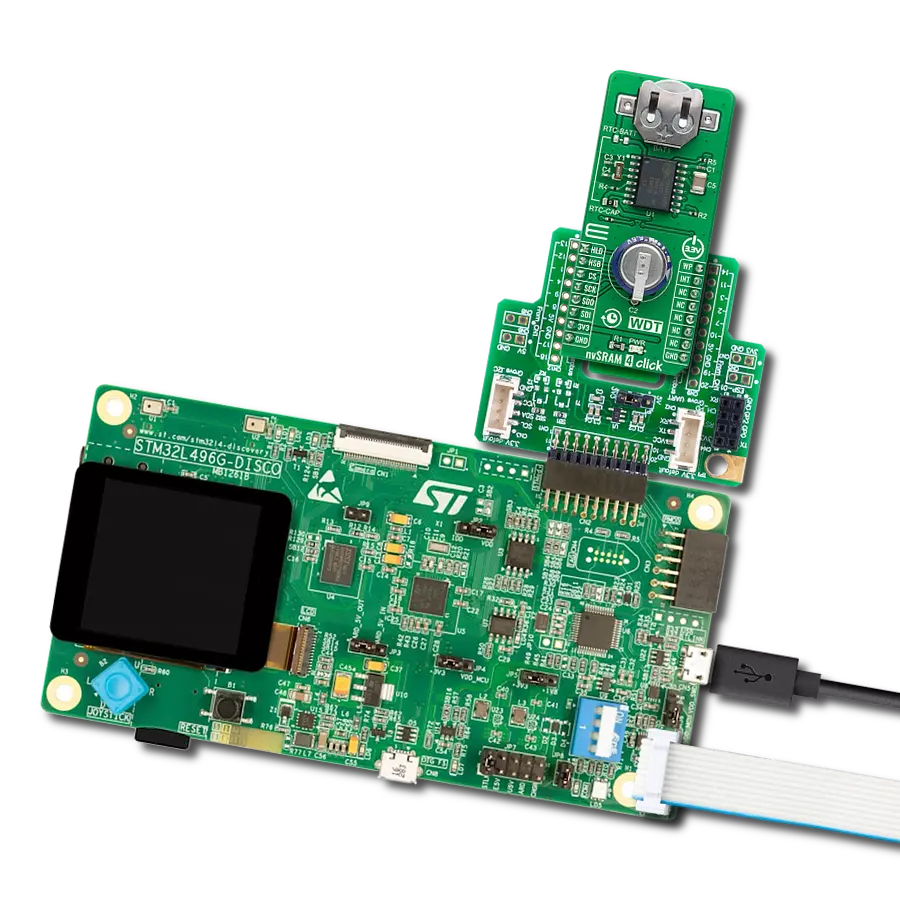

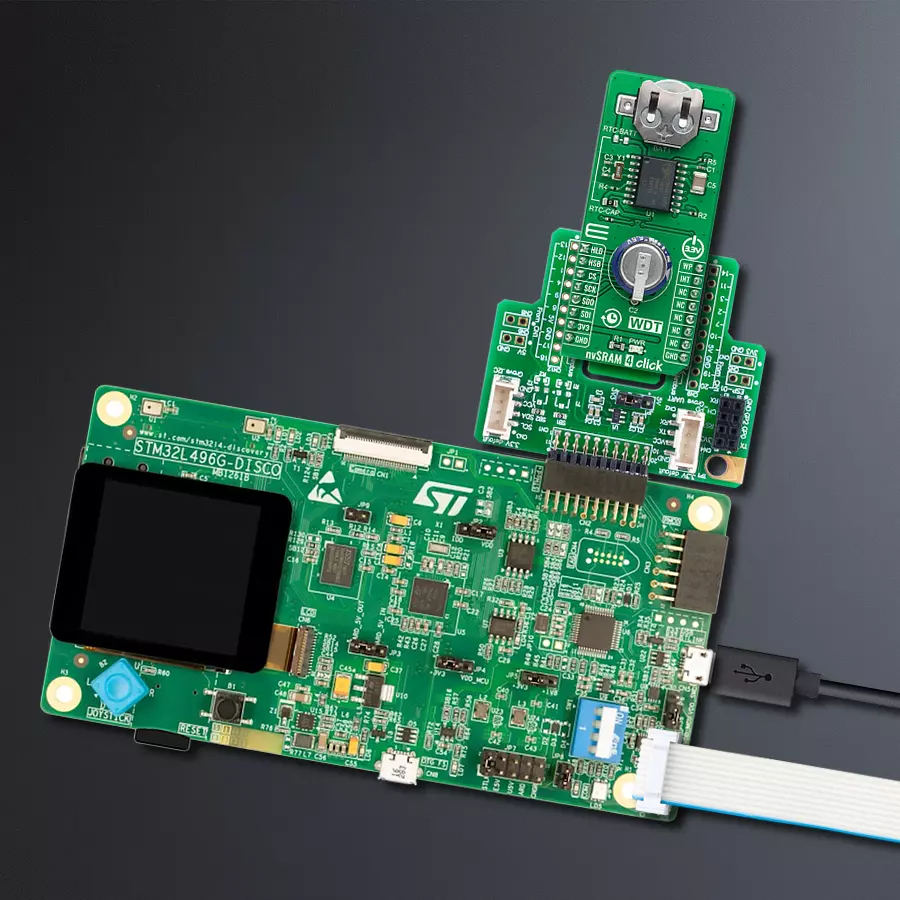

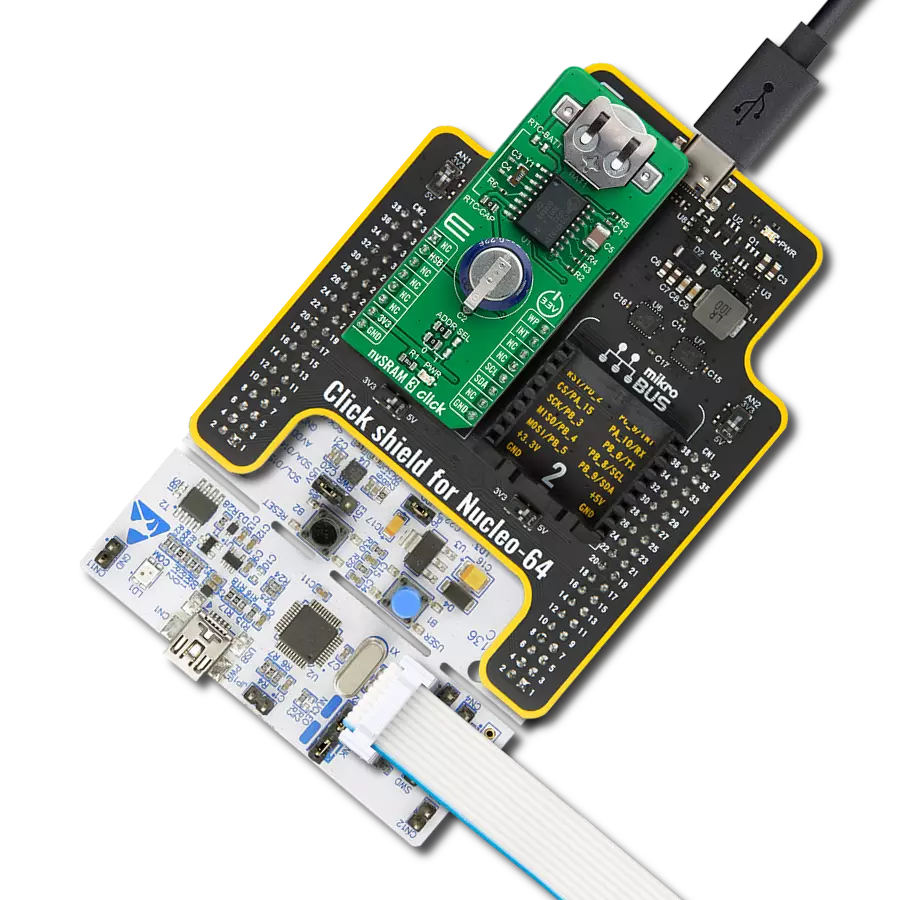

nvSRAM 4 Click is based on the CY14B101PA, a 1-Mbit nvSRAM memory organized as 128K words of 8 bits each, with a fully-featured real-time clock from Infineon. The nvSRAM specifies one million endurance cycles for nonvolatile cells with data retention of a minimum of 20 years. All the reads and writes to nvSRAM happen to the SRAM, which gives nvSRAM the unique capability to handle infinite writes to the memory. The benefit of nvSRAM over serial EEPROMs is that all reads and writes to nvSRAM are performed at the SPI speed with zero cycle delay, which means, therefore, no wait time is required after any of the memory accesses. In addition to the CY14B101PA, this Click board™ is equipped with the button cell battery holder compatible with the 3000TR battery holder, suitable for 12mm Coin Cell batteries. When the primary power fails and drops below 2.65V, this Click board™ switches to the backup power supply by placing a jumper labeled as RTC-BATT. By utilizing an automatic backup, the CY14B101PA uses an external battery power source when there is no power supply on its main power terminals, allowing for uninterrupted operation. nvSRAM 4

Click communicates with MCU using a standard SPI interface with clock frequency up to 40MHz, zero cycle delay read, and write cycles. It also supports the two most common modes, SPI Mode 0 and 3, and 104 MHz SPI access speed with special instructions for the read operation. The CY14B101PA uses the standard SPI opcodes for memory access. In addition to the general SPI instructions for reading and writing, it provides four special instructions: STORE, RECALL, AutoStore Disable (ASDISB), and AutoStore Enable (ASENB). The STORE operation of the CY14B101PA can be controlled and acknowledged via the HSB pin, routed on the RST pin of the mikroBUS™ socket. If no STORE/RECALL is in progress, this pin can request a hardware STORE cycle. When the HSB pin is driven LOW, the CY14B101PA initiates a STORE operation conditionally. Also, this Click board™ can use the AutoStore feature of the SRAM data in nonvolatile cells when the power goes down, providing power-down data security by placing a jumper labeled as RTC-CAP. An additional feature of this Click board™ represents the configurable Write Protection function labeled

as WP routed on the PWM pin of the mikroBUS™ socket. The WP pin protects the entire memory and all registers from write operations and must be held high to inhibit all the write operations. When this pin is high, all memory and register writes are prohibited, and the address counter is not incremented. Besides, the nvSRAM 4 Click also has additional HOLD and Interrupt pins, routed to the AN and INT pins of the mikroBUS™ socket labeled as HLD and INT. The HLD pin is used to pause the serial communication without stopping the operation of the write status register, programming, or erasing in progress. On the other hand, an INT pin can be used in several ways, such as interrupt output, calibration, or a square wave, programmable to respond to the clock alarm, the watchdog timer, and the power monitor. This Click board™ can be operated only with a 3.3V logic voltage level. The board must perform appropriate logic voltage level conversion before using MCUs with different logic levels. Also, it comes equipped with a library containing functions and an example code that can be used as a reference for further development.

Features overview

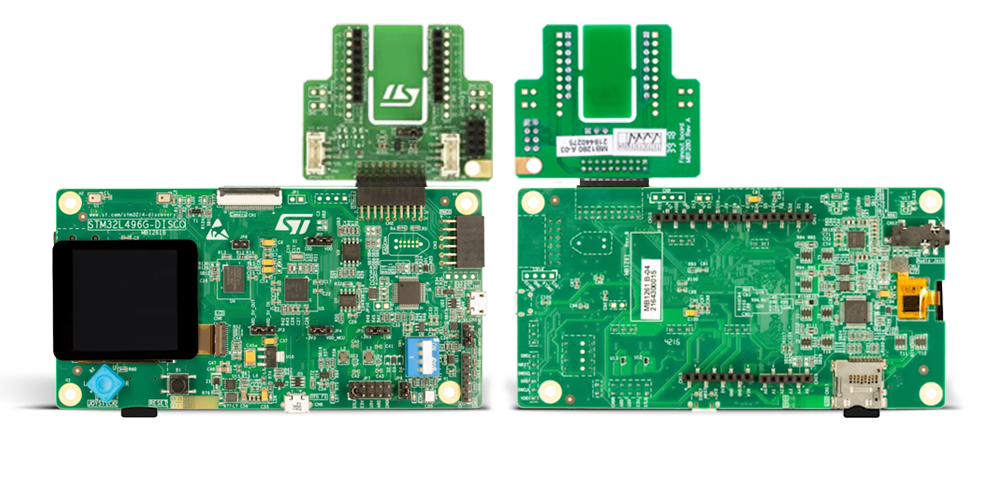

Development board

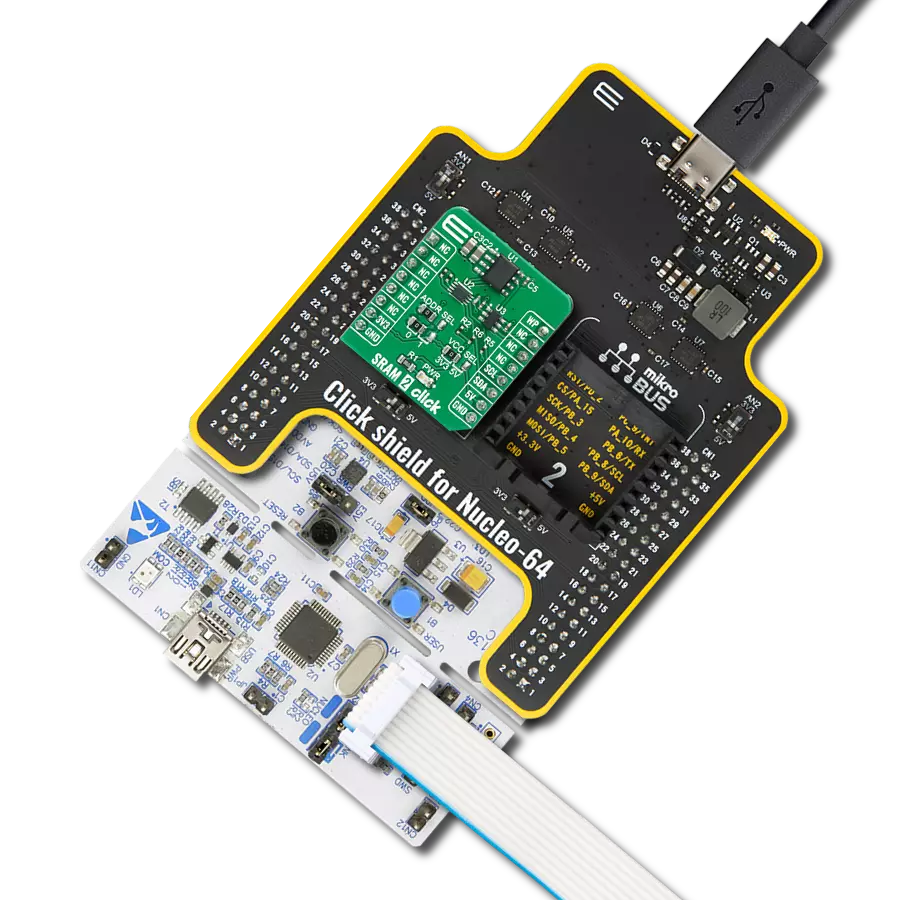

The 32L496GDISCOVERY Discovery kit serves as a comprehensive demonstration and development platform for the STM32L496AG microcontroller, featuring an Arm® Cortex®-M4 core. Designed for applications that demand a balance of high performance, advanced graphics, and ultra-low power consumption, this kit enables seamless prototyping for a wide range of embedded solutions. With its innovative energy-efficient

architecture, the STM32L496AG integrates extended RAM and the Chrom-ART Accelerator, enhancing graphics performance while maintaining low power consumption. This makes the kit particularly well-suited for applications involving audio processing, graphical user interfaces, and real-time data acquisition, where energy efficiency is a key requirement. For ease of development, the board includes an onboard ST-LINK/V2-1

debugger/programmer, providing a seamless out-of-the-box experience for loading, debugging, and testing applications without requiring additional hardware. The combination of low power features, enhanced memory capabilities, and built-in debugging tools makes the 32L496GDISCOVERY kit an ideal choice for prototyping advanced embedded systems with state-of-the-art energy efficiency.

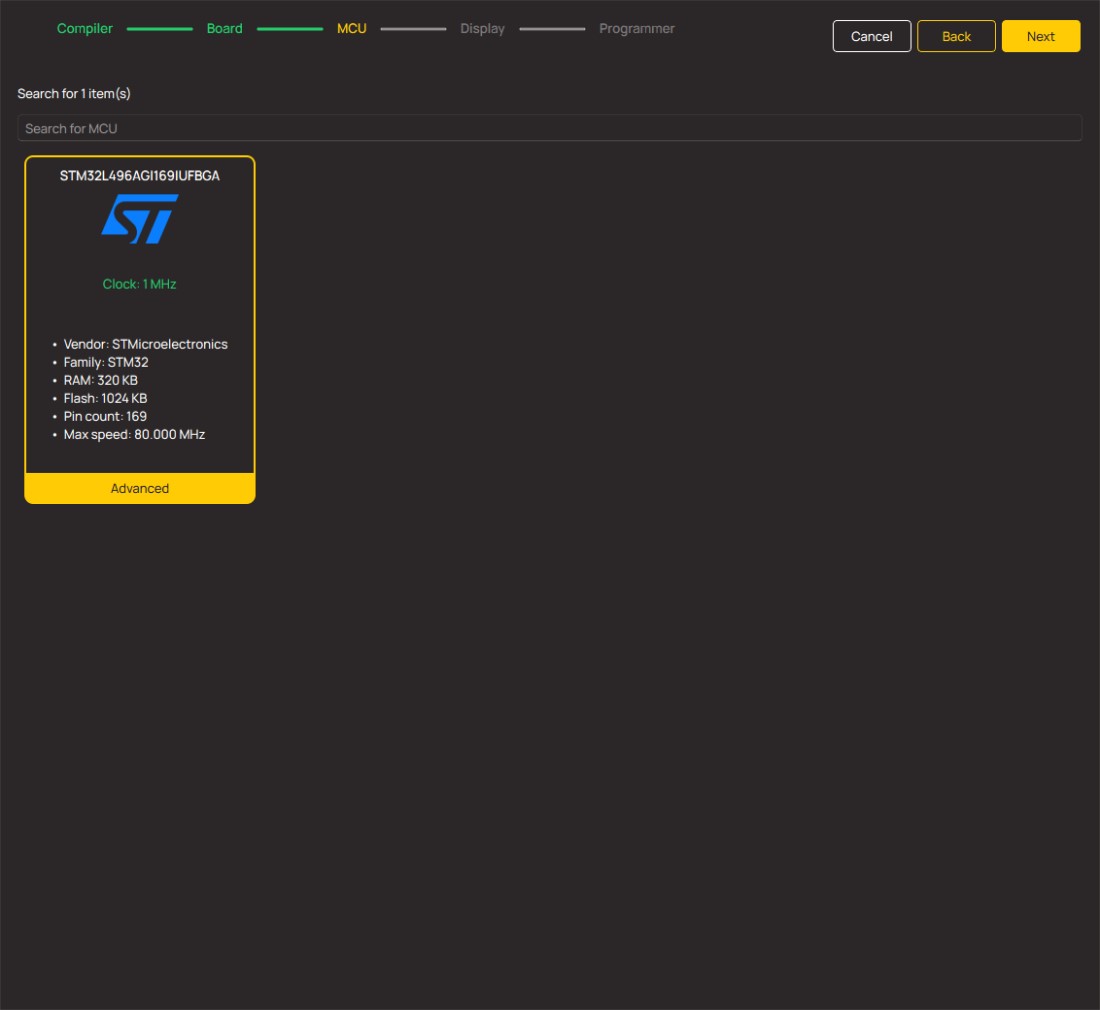

Microcontroller Overview

MCU Card / MCU

Architecture

ARM Cortex-M4

MCU Memory (KB)

1024

Silicon Vendor

STMicroelectronics

Pin count

169

RAM (Bytes)

327680

Used MCU Pins

mikroBUS™ mapper

Take a closer look

Click board™ Schematic

Step by step

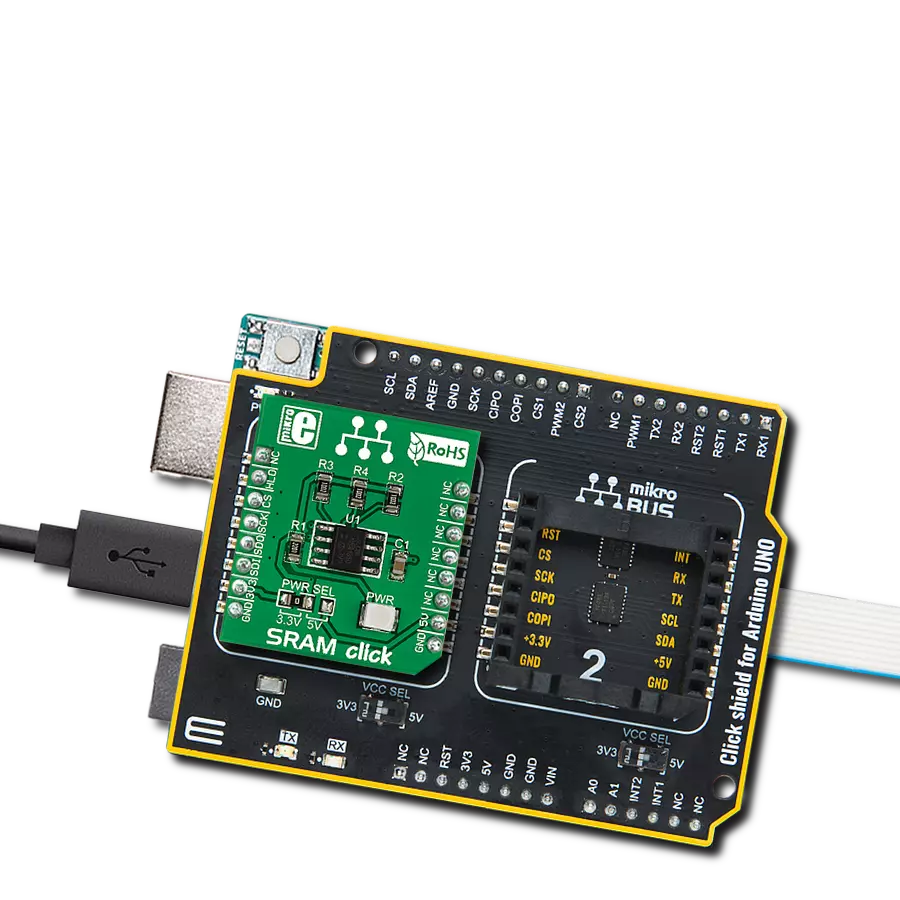

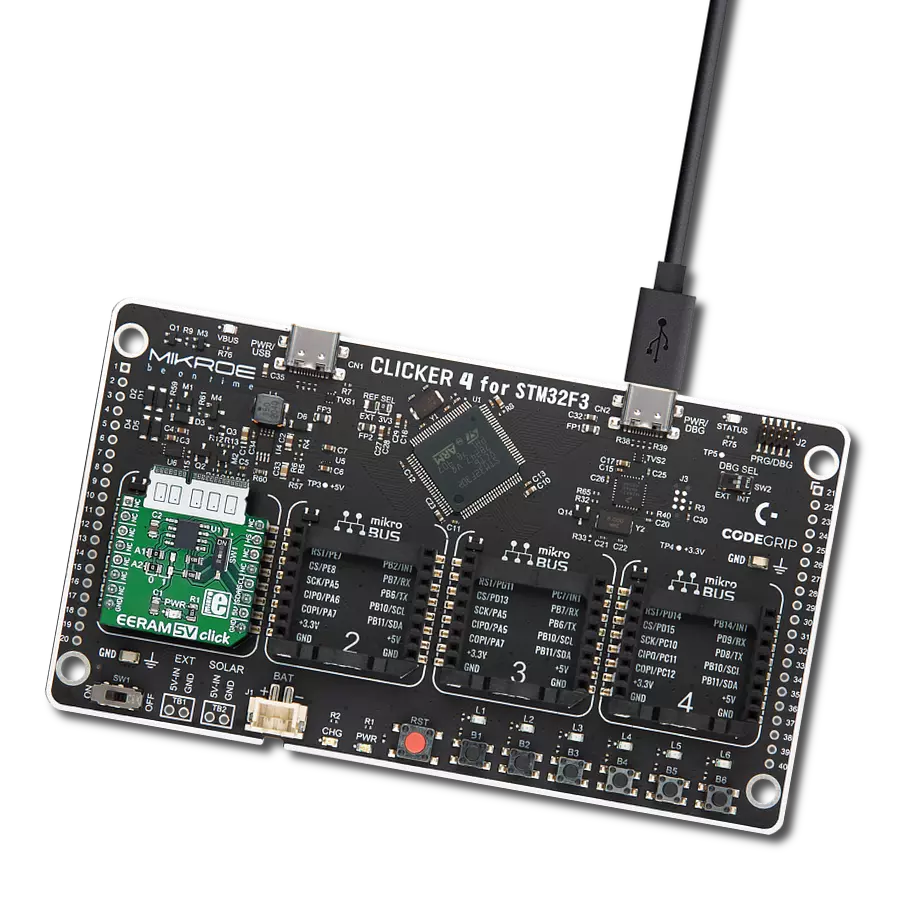

Project assembly

Software Support

Library Description

This library contains API for nvSRAM 4 Click driver.

Key functions:

nvsram4_burst_read_memory- nvSRAM 4 burst read memory function.nvsram4_burst_write_memory- nvSRAM 4 burst write memory function.nvsram4_get_rtc_time- nvSRAM 4 get RTC time function.

Open Source

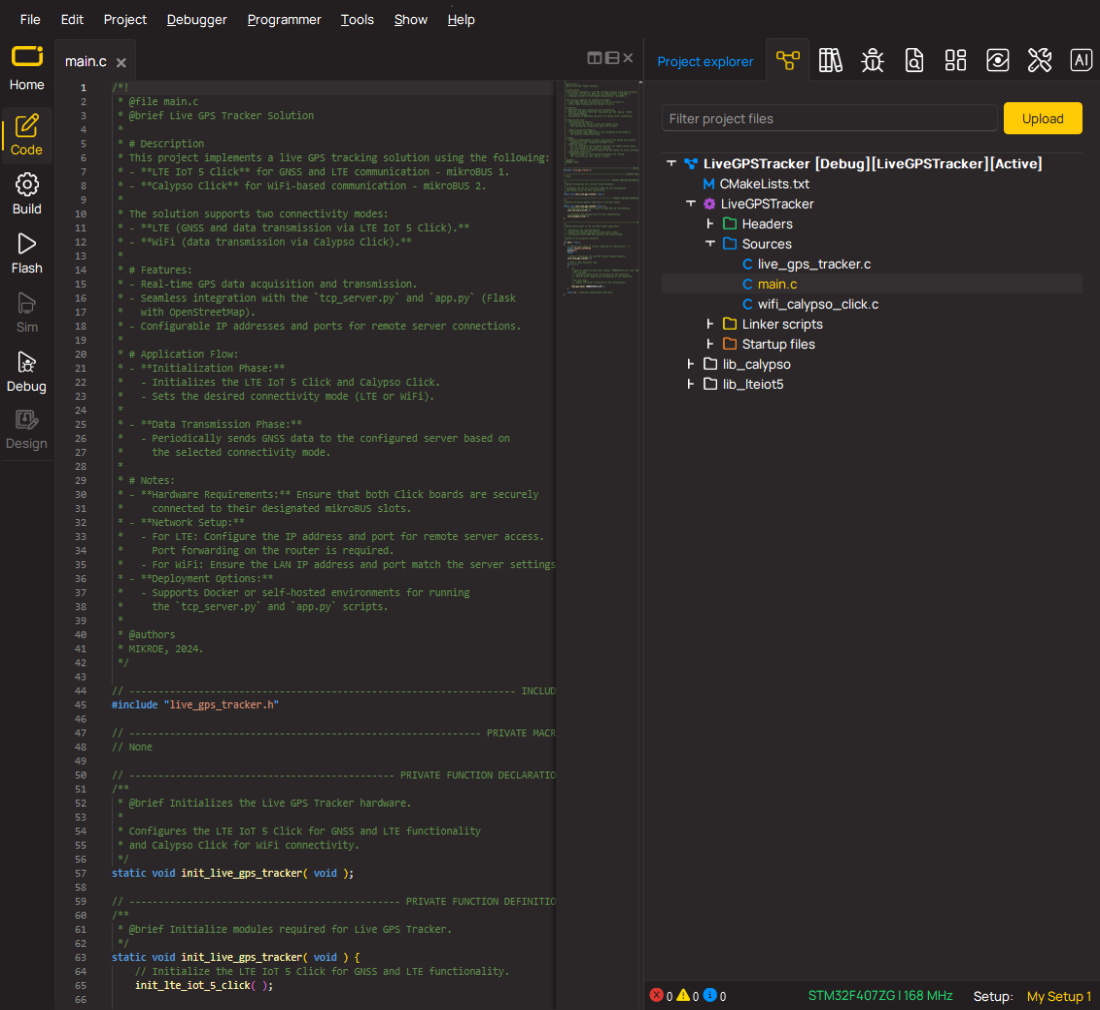

Code example

The complete application code and a ready-to-use project are available through the NECTO Studio Package Manager for direct installation in the NECTO Studio. The application code can also be found on the MIKROE GitHub account.

/*!

* @file main.c

* @brief nvSRAM4 Click example

*

* # Description

* This is an example that demonstrates the use of the nvSRAM 4 Click board.

*

* The demo application is composed of two sections :

*

* ## Application Init

* Initialization driver enables - SPI,

* write demo_data string ( mikroE ), starting from the selected memory_addr ( 112233 ),

* set the time to 12:30:31 and set the date to 31-12-20.

*

* ## Application Task

* In this example, we read a data string, which we have previously written to memory,

* starting from the selected memory_addr ( 112233 )

* and read and display the current time and date, which we also previously set.

* Results are being sent to the Usart Terminal where you can track their changes.

* All data logs write on USB uart changes for every 1 sec.

*

* @author Nenad Filipovic

*

*/

#include "board.h"

#include "log.h"

#include "nvsram4.h"

static nvsram4_t nvsram4;

static log_t logger;

static char demo_data[ 9 ] = { 'm', 'i', 'k', 'r', 'o', 'E', 13 ,10 , 0 };

static char rx_data[ 9 ];

static uint32_t memory_addr;

static uint8_t new_sec = 255;

static uint8_t c_year = 20;

static nvsram4_rtc_time_t time;

static nvsram4_rtc_date_t date;

void application_init ( void ) {

log_cfg_t log_cfg; /**< Logger config object. */

nvsram4_cfg_t nvsram4_cfg; /**< Click config object. */

/**

* Logger initialization.

* Default baud rate: 115200

* Default log level: LOG_LEVEL_DEBUG

* @note If USB_UART_RX and USB_UART_TX

* are defined as HAL_PIN_NC, you will

* need to define them manually for log to work.

* See @b LOG_MAP_USB_UART macro definition for detailed explanation.

*/

LOG_MAP_USB_UART( log_cfg );

log_init( &logger, &log_cfg );

log_printf( &logger, "\r\n" );

log_info( &logger, " Application Init " );

// Click initialization.

nvsram4_cfg_setup( &nvsram4_cfg );

NVSRAM4_MAP_MIKROBUS( nvsram4_cfg, MIKROBUS_1 );

err_t init_flag = nvsram4_init( &nvsram4, &nvsram4_cfg );

if ( init_flag == SPI_MASTER_ERROR ) {

log_error( &logger, " Application Init Error. " );

log_info( &logger, " Please, run program again... " );

for ( ; ; );

}

nvsram4_default_cfg ( &nvsram4 );

Delay_ms ( 100 );

log_info( &logger, " Application Task " );

log_printf( &logger, "-----------------------\r\n" );

log_printf( &logger, " nvSRAM 4 Click \r\n" );

log_printf( &logger, "-----------------------\r\n" );

memory_addr = 112233;

nvsram4_set_cmd( &nvsram4, NVSRAM4_STATUS_WREN );

Delay_ms ( 100 );

log_printf( &logger, " Write data : %s", demo_data );

nvsram4_burst_write_memory( &nvsram4, memory_addr, &demo_data[ 0 ], 9 );

log_printf( &logger, "-----------------------\r\n" );

Delay_ms ( 1000 );

date.day_of_week = 4;

date.day = 31;

date.month = 12;

date.year = 20;

nvsram4_set_rtc_date( &nvsram4, date );

Delay_ms ( 100 );

time.hours = 23;

time.min = 59;

time.sec = 50;

nvsram4_set_rtc_time( &nvsram4, time );

Delay_ms ( 100 );

}

void application_task ( void ) {

nvsram4_get_rtc_time( &nvsram4, &time );

Delay_ms ( 1 );

nvsram4_get_rtc_date( &nvsram4, &date );

Delay_ms ( 1 );

if ( time.sec != new_sec ) {

log_printf( &logger, " Date : %.2d-%.2d-%.2d\r\n", ( uint16_t ) date.day, ( uint16_t ) date.month, ( uint16_t ) date.year );

log_printf( &logger, " Time : %.2d:%.2d:%.2d\r\n", ( uint16_t ) time.hours, ( uint16_t ) time.min, ( uint16_t ) time.sec );

log_printf( &logger, "- - - - - - - - - - - -\r\n" );

new_sec = time.sec;

Delay_ms ( 10 );

if ( date.year != c_year ) {

log_printf( &logger, " Happy New Year \r\n" );

c_year = date.year;

Delay_ms ( 10 );

} else {

nvsram4_burst_read_memory( &nvsram4, memory_addr, &rx_data[ 0 ], 9 );

log_printf( &logger, " Read data : %s", rx_data );

}

log_printf( &logger, "-----------------------\r\n" );

} else {

Delay_ms ( 1 );

}

}

int main ( void )

{

/* Do not remove this line or clock might not be set correctly. */

#ifdef PREINIT_SUPPORTED

preinit();

#endif

application_init( );

for ( ; ; )

{

application_task( );

}

return 0;

}

// ------------------------------------------------------------------------ END

Additional Support

Resources

Category:SRAM